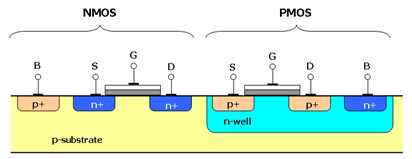

문턱전압(Threshold Voltage): Strong Inversion 상태를 만들 수 있게 해주는 최소한의 전압. (Switching Voltage)-구성요소 -문턱 전압 측정법1. Linear Extrapolation 2. Constant Current3. gm Method: I-V 그래프를 미분하여서 구하는 방법. -문턱 전압 조절 방법-- 을 조절: 일반적으로 Metal 일함수를 조절 (Poly Si 사용, HKMG시 Metal 사용)NMOS는 일함수가 낮은 금속, PMOS는 일함수가 높은 금속을 이용 (Dual Metal Gate 공정) --기판농도 변경: 기판 전체의 농도를 변경하기보단 표면만 농도조절 (Vth adjust implant 공정)--Oxide (커패시터 용량)..