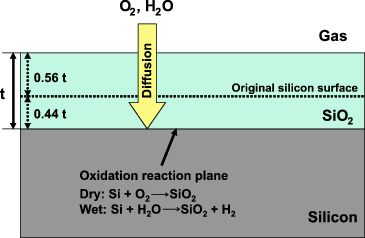

산화막 생성 Cycle (Oxidation)1. Push (Loading) Thermal Stress 최소화를 위해 저온 시작, Nitride 형성 방지를 위해 O2 일부 Flow2. Ramp Up 온도 서서히 증가3. Oxidation 4. Ramp Down Stress와 Surface State를 낮추고 Fixed Charge 억제5. N2 Anneal and Pull (Unloading) 전기적 Defect in Thermal Oxide1. Mobile Charge (Qm)Oxide 막 내에 존재하는 이온에 의한 Charge, 알칼리 금속(K+, Na+, Li+ 등) 이온의 오염이 원인고온, 고전압 상태에서 동작할 때 소자의 문턱전압의 불안정 또한 원인Oxidation공정에서 Cl gas를 추가해..