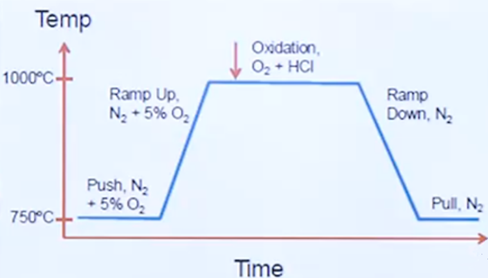

산화막 생성 Cycle (Oxidation)

1. Push (Loading) Thermal Stress 최소화를 위해 저온 시작, Nitride 형성 방지를 위해 O2 일부 Flow

2. Ramp Up 온도 서서히 증가

3. Oxidation

4. Ramp Down Stress와 Surface State를 낮추고 Fixed Charge 억제

5. N2 Anneal and Pull (Unloading)

전기적 Defect in Thermal Oxide

1. Mobile Charge (Qm)

Oxide 막 내에 존재하는 이온에 의한 Charge, 알칼리 금속(K+, Na+, Li+ 등) 이온의 오염이 원인

고온, 고전압 상태에서 동작할 때 소자의 문턱전압의 불안정 또한 원인

Oxidation공정에서 Cl gas를 추가해 제거

2. Oxide Trapped Charge (Qot)

Bulk 산화막 내에 Carrier가 포획된 상태, 불순물이나 Broken Bonds와 같은 산화막 내 결함이 원인.

고에너지 Carrier나 방사선에 의해서도 발생

3. Fixed Oxide Charge (Qf)

Si/SiO2계면에서 35A 이내에 영역에 존재하는 이온화된 Si(양이온),

Cooling시 낮은 온도에서 산화 공정이 이뤄질 때 발생,

Cooling 시간을 단축하면 개선되지만 새로운 Warpage(뒤틀림)나 Slip이 발생할 수 있음

4. Interface Trapped Charge (Qit)

Oxide의 Si-O 결합이 끊어진 것. 산화로 인한 구조적 결함이나 금속 불순물로 발생,

H 로 Dangling Bond를 Passivation하거나 Annealing(수소, 질소, 아르곤 등)을 통해 안정화

'반도체 > 산화막 증착 (Oxidation)' 카테고리의 다른 글

| [산화막 증착] 산화 공정을 사용하는 이유 (0) | 2024.08.26 |

|---|---|

| [산화막 증착] 산화막이란? 산화막의 생성 방법! (0) | 2024.07.03 |