산화막을 사용하는 이유는 크게 3가지로 나눌 수 있습니다.

1)소자와 소자를 나누기 위해(격리, Isolation)

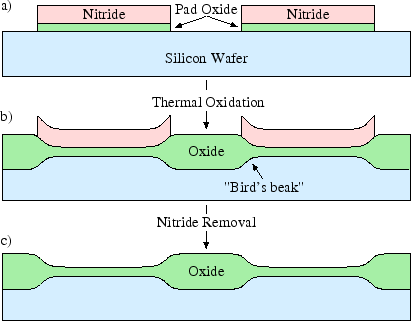

-LOCOS (Local Oxidation of Silicon)

소자 양쪽에 산화 공정을 통해 Isolation, 평평하지 않고 소자영역을 침범하기 때문에 미세화에 부적합

+Bird`s Beak 현상: 새의 부리처럼 가장자리는 조금 형성되고 가운데 부분은 두껍게 형성되는 현상.

이로 인해 Vth가 증가하게 됨. Gate Length가 늘어났기 때문에 더 많은 전압을 가해줘야 함.

-> 실리콘을 조금 Etching해 튀어나오는 부분을 최소화할 수 있음

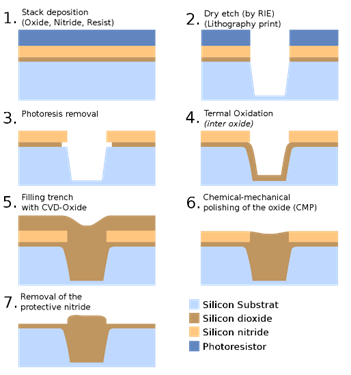

-STI(Shallow Trench Isolation=얕고 넓게)

Etching 공정을 통해 Isolation 할 부분을 미리 식각 후 산화막을 증착.

미세화에 적합하나 비등방성 어려움. CMP 공정 진행.

1. Oxide, Nitride, Resist Depo.

2. Dry Etch(RIE)로 Trench 형성

3. PR Removal (Ashing 공정)

4. Thermal Oxidation (Barrier 역할, HDPCVD에 의한 손상 방지)

5. Filling Trench with CVD (Filling Oxide with HDPCVD

6. CMP

7. Nitride Removal

=>DTI(Deep Trench Isolation) 더 깊게 파는 공정

Barrier Oxide 외에도 Linear Nitride를 활용해 Stress 제어

2)Mask 역할

-Photo나 Ion Implantation 시 Mask로 사용 가, B보단 P일때, 온도가 높을 때 두꺼워야 함.

3)절연체 역할 (Oxide는 큰 값, Insulator로는 작은 값)

-Gate 절연체: MOSFET에서 Gate와 Si 사이에 절연체로 사용. (SiO2의 한계로 HfO2로 변경하는 추세)

-Passivation: PN Junction을 보호

-IMD(Inter Metal Dielectric): Metal과 Metal 사이, Metal과 Via(길)사이 절연, 지지대 역할.

-ILD(Inter Layer Dielectric): Metal과 Si사이의 절연, Contact간의 절연, 지지대 역할.

=> IMD와 ILD는 CMP 공정 필수!

'반도체 > 산화막 증착 (Oxidation)' 카테고리의 다른 글

| [산화막 증착] 산화 공정 심화. 생성 Cycle, 전기적 Defects (0) | 2024.08.26 |

|---|---|

| [산화막 증착] 산화막이란? 산화막의 생성 방법! (0) | 2024.07.03 |