Short Channel Effect (SCEs) :여러가지이기 때문에 주로 복수형으로 사용

MOSFET을 미세화 하면서 발생하는 단점. 소자의 목적 - Vg에 의해서만 Current가 제어되는 것! 대부분 Drain 전압의 문제

-미세화 장점: 속도 증가, 커패시턴스 감소, 원가 감소, 칩사이즈 감소.

-미세화 단점 = SCE

(1) Vth Roll Off

Channel이 짧아지며 S/D Depletion 영역과 Channel 영역이 겹치게 되고,

겹치는 부분에서 Charge가 공유(Charge Sharing).

이 Charge는 채널이 짧아지면서 포함되는 비율이 증가하고,

Depletion영역의 불순물 음의 값으로 되어 있기 때문에

Gate 전압을 크게 인가하지 않아도 쉽게 Channel 형성에 필요한 전압이 충족되어

문턱 전압이 원하지 않는 값으로 작아지고, 원하지 않는 값으로 Drain Current가 증가함.

문턱 전압이 낮아지면서 Leakage가 증가하고, Gate Voltage의 Control 능력이 감소함. DIBL도 발생 가능

개선: Shallow Junction Depth Profile

(2) DIBL (Drain Induced Barrier Lowering)

Drain에 전압을 가할 때 전압이 클수록 Drain 쪽 Depletion 영역이 증가하고,

전계가 강해지면서 Depletion영역이 Channel 침범. (Vth Roll Off)

이때 감소 Vth 그래프에서 기울기를 보면, Long보다 Short에서 더 작은 값을 가짐

Vth가 작아졌다고 좋아진 것이 아니라 게이트 구동력이 Depletion Cap에 의해 감소.

Source에서 Drain으로 Carrier가 넘어가기 위한

Barrier(Source-Channel Potential)가 낮아져 Vth감소/Leakage 증가.

Barrier는 S와 D가 가까워질수록 더 많이 감소함.

Vg로 제어되는 것이 아니라 Vd로 제어가 되는 것이기 때문에 문제. (둘 다 영향이 있긴 함)

(단위 V/V, mV/V – VD의 변화량 당 Vt변화량)

++보통의 상황에서는 Vth가 감소하는 쪽이 소자의 Performance에 좋지만,

Off Current를 최소화하고, On Current를 최대화시키면서 해야함.

즉, Slope가 커져야 하지만 60mV/dec이라는 한계가 있기 때문에

FinFET, GAA 등의 새로운 구조의 소자가 개발.

개선:

FinFET

SOI Wafer

LDD(Lightly Doped Drain): Drain(n+) 쪽에 n를 약하게 도핑하여 S와 D간에 농도 차이를 줄여 전계를 낮춤

기판 효과(Body Effect) 감소, Vth Roll Off 완화. But 낮은 도핑 농도로 기생저항이 생겨 On Current 감소할 수 있음.

=>Gate Spacer 공정 필요.

+Gate Spacer: LDD를 만들기 위해 Gate 단자를 Side Wall 형태의 절연체로 둘러싸는 구조(이온 주입의 방패)

-Doping

1. 기판과 S/D 사이의 도핑 농도를 줄이면서 Oxide의 두께를 줄여 Cap의 값을 늘려야 함.

2. Retrograde Body Doping Profile 이용.

(3) Velocity Saturation

Channel이 짧아지면서 전계가 강하게 걸려 Carrier의 속도가 매우 빨라지는 현상.

소자 내 열 발생->Lattice Scattering증가->Carrier 충돌 증가->Mobility 감소=증가할 것으로 예상되던 전류가 낮은 전류 값에서 Saturation.

(Performance 향상 어려움, PMOS의 경우 NMOS보다 Mobility가 낮아 더욱 잘 일어남)

개선: 전계 완화! LDD

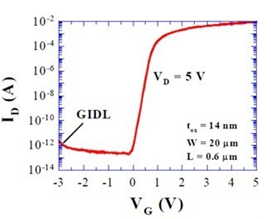

(4) GIDL (Gate Induced Drain Leakage) Vd만으로 Energy Band의 심한 Bending 발생

Cox를 개선을 위한 얇은 산화막과 Gate 전압에 의해 형성된 강한 전계가 Drain 쪽 터널링을 형성해 Leakage발생. (Subthreshold Current)

Drain의 Valance Band의 최외각 전자들이 Source의 Conduction Band로 넘어가는 Bend to Bend Tunneling으로 Leakage 발생

Vg가 강한 음전압, Vd가 강한 양전압을 가질수록 전계가 강해짐.

=>해결: 전계를 완화시켜줘야 함. 즉, Doping Profile 변경.

-LDD

-Spacer

+소자 열화 특성: Oxide에 Carrier가 Trap 되어 Vth 증가, Id 감소, Leakage

1. NBTI(Negative Bias Thermal Instability)

- PMOS에 Negative bias를 인가해 Stress를 주었을 때 Subthreshold Current

2. PBTI((Positive Bias Thermal Instability)

- NMOS에 Positive bias를 인가해 Stress를 주었을 때 Subthreshold Current

3. HCI - 아래 참고

(5) HCI (Hot Carrier Injection)

Vg가 Saturation Voltage값을 가질 때 Channel이 짧아짐에 따라 Pinch Off로 인한 전계가 강해져

Drain으로 이동하는 Carrier는 너무 많은 에너지를 받아 가속

Carrier 가Gate로 끌어당겨지면서 Gate Oxide에 Trap되어 Vth 증가,

Depletion 영역에서 Impact Ionization이 발생해 Subthreshold Current 가 증가.

MOSFET 수명 단축, Oxide와 Si계면이 Carrier에 의해 결합이 파괴되어 Interface State와 기생 Cap이 증가해 SS가 증가

=>해결: 전계 완화 -Spacer -LDD -Drain 도핑 농도 감소: 전계가 감소되나 S와 D의 저항이 증가해 D 전류가 줄어들어 Performance 감소

-Vg 증가: Vg가 증가하면 Channel의 Carrier가 증가하고, Pinch Off의 영역이 감소해 HCI을 감소시킴.

++Impact Ionization (Avalanche Breakdown 발생)

가속된 Hot Carrier들이Pinch Off 영역에 형성된 결정격자와 충돌하면서 Si가 이온화되는 EHP(Electron Hole Pair)가 증가하고,

생성된 EHP들은 또다시 가속되어 무수히 많은 EHP를 눈사태처럼 만들어내 Subthreshold Current 증가

(Hole이 Sub으로 유입되는 모양이 종 모양과 비슷하다 하여 Bell Shape 현상이라고도 함.)

(6) Punch Through

미세화로 S와 D의 Depletion Region이 만나 Vd에 의해 S에서 D로 전류가 급증.

특히, 접합부 Edge에 전계가 집중되어 Depletion증가

Channel을 이용하지 않음. 즉, Vg에 관계없이 흐르는 현상 (Leakage)

S와 D가 가까울수록, Channel이 짧을수록 잘 발생. 정확한 On/Off 동작을 하지 못함

=>해결: Depletion 영역의 확장을 제어.

SOI Wafer Body의 Charge Path를 제거

Halo Implant = Pocket Implant (Punch Through Stop Implant)

Source/Drain 코너 부분에 기판 농도(NMOS 기준 P+)를 고농도로 국부적으로 높이는 방법.

Depletion영역이 기판 쪽으로 확장하는 것을 억제함. (농도 차이를 줄임)

Shallow Junction Depth Profile

Source와 Drain을 얕게 추가 Doping해 Depletion영역이 수평으로 확장되는 것을 제어

-고온에서 짧은 시간의 Annealing이 필요함! 무거운 이온을 사용하고 낮은 이온에너지가 필요함

S/D의 저항성분이 증가해 출력 특성이 저하되기도 함.

-> 개선: Raised S/D

- S/D를 수직으로 성장시킴, SOI에도 사용

Depletion 영역은 도핑 농도가 작은 쪽으로 더 넓게 형성.

주로 기판의 농도가 작기 때문에 기판 쪽으로 더욱 확장.

Halo Implant의 목적이 이 원리를 이용

'반도체 > Wafer 및 소자(Device) 기초' 카테고리의 다른 글

| [Epitaxy] Epitaxy 공정 (3) | 2024.09.02 |

|---|---|

| [CMOS] CMOS, 유전체, 유전률 (0) | 2024.09.02 |

| [Junction] Ohmic과 Schottky 접합 (0) | 2024.09.02 |

| [Energy Band] Energy Band와 Band Gap (1) | 2024.08.29 |

| [Wafer 공정] Wafer 준비 - 쵸크랄스키 방법, Ingot, OHT (2) | 2024.07.02 |