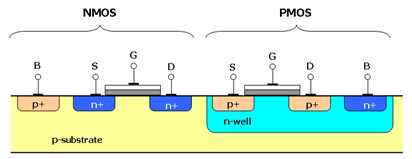

PMOS와 NMOS의 차이점 => CMOS

전자(Electron)의 Mobility가 정공(Hole)의 Mobility보다 2.7배 큼. 즉, NMOS가 더 빠름

->CMOS (Complementary MOS) 가 나오게 된 배경. (Inverter로 주로 사용)

NMOS는 크기는 작으나 저항에 의한 Leakage발생.

이 저항 대신 PMOS를 이용해 제어를 하며 Leakage 차단.

소비전력이 낮고, 출력 특성도 좋지만 조금 느리다. 집적도가 높음. BJT에 비해 회로도 간단

NMOS는 Gate에 양전압이 들어왔을 때 활성화되며 Source의 LOW Level Voltage를 Drain으로 출력

PMOS는 Gate에 음전압이 들어왔을 때 활성화되며 Source의 HIGH Level Voltage를 Drain으로 출력

양전압이든 음전압이든 두 MOS중 한가지는 항상 켜지며, 동시에 켜질 순 없음.

여기서 효율적으로 CMOS를 사용하기 위해선 NMOS와 PMOS의 특성이 대칭적으로 비슷해야 좋음.

즉, PMOS가 느리므로 Channel Length를 NMOS보다 길게 설정하면서 제어함.

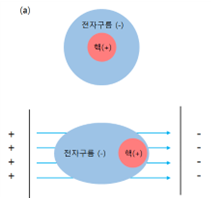

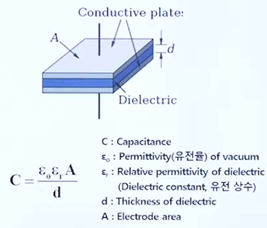

++Dielectric: 유전체, 절연물질을 전계 중간에 두게 되면 표면에 전하가 나타나는 물질

++Permittivity: 유전율, 유전체 분극 척도. MOSFET에서 Channel이 형성되기 위해선 분극이 많이 생길수록 전하가 잘 모여 유리함.

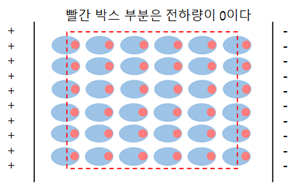

유전체에 전기장을 가하면 유전 분극이 일어나 반대방향으로 전계가 형성되어 전기장 세기가 작아 짐. 이 비율이 유전율.

너무 높으면 Leakage가 생길 수 있는 Trade Off 관계. (중간 값인 Hf를 이용하는 이유.). 실리콘(11.7)과 산화막(3.9)의 비율은 정확히 3.

1. 클수록 전기 에너지가 잘 전달된다. == 분극이 잘 일어난다. Band Gap이 작다. Leakage가 잘 발생한다. Capacitor의 저장 용량이 큼

2. 작을수록 절연이 잘 된다. == 기생 Capacitor 용량 감소. Leakage 감소. Device 속도 증가, 전기신호 원할, 전력 필요량 감소

| 유전율 | BandGap | |

| SiO2 | 3.9 | 9.1 |

| TiO2 | 83~100 | 3.05 |

| HfO2 | 20~25 | 5.8 |

Capacitance (커패시턴스, 전기 용량)

전하가 대전되어 있는 대전체에서 전압 당 전하량 총 합의 비

'반도체 > Wafer 및 소자(Device) 기초' 카테고리의 다른 글

| [Transistor] Transistor, 트렌지스터 (4) | 2024.09.02 |

|---|---|

| [Epitaxy] Epitaxy 공정 (3) | 2024.09.02 |

| [Short Channel Effect] Short Channel Effect, SCEs (0) | 2024.09.02 |

| [Junction] Ohmic과 Schottky 접합 (0) | 2024.09.02 |

| [Energy Band] Energy Band와 Band Gap (1) | 2024.08.29 |