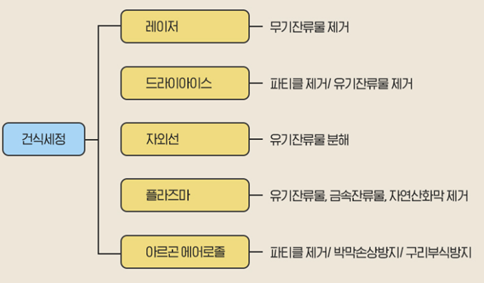

1. Wet Cleaning DI Water 세정에 용이하고, 다양한 화학 용액을 사용 가능하며 Selectivity가 매우 우수. Dry Cleaning 대비 저렴하고, Particle 제거에 효과적하지만, 세정의 건조가 느려 잔유물이 남을 수 있으며, 물질의 독성이 위험하고, 용액을 폐기하는 비용이 추가.진공상태 유지가 어렵기 때문에 2차 오염 문제 발생 가능. 공정이 미세화 됨에 따라 Dry를 사용하는 추세. (아직은 Wet이 메인)++ RCA (Radio Corporation of America) Cleaning: 표준 세정법1) SC-1 (APM, Ammonium Peroxide Mixture) (NH4OH : H2O2 : H2O)Lift Off를 통해 파티클을 이격 시킨 뒤 재흡착을 방지하기 ..