High K Metal Gate (HKMG) (<->Low K: 전하를 잡아 두는 힘이 약해 배선 공정 Short 방지, RC Delay 방지)

Device의 미세화에 따라 Gate Length가 짧아지면서 수평방향의 전기장이 너무 강해 수직적인 방향의 전기장(Gate가 만드는)이 약해짐.

이를 위해 산화막의 두께를 줄여 Cox(Cap)를 키워야 함->이미 너무 작은 값을 사용해 한계(Gate Leakage 발생)

=>유전율이 높은 HfO2를 사용하게 되었지만 Vth가 증가하고 전자의 Mobility가 감소하는 단점 발생.

또한, Poly Si와 High K 산화막은 저항이 높아지고 Oxide Cap을 감소시킴.

이를 위해 Poly Si 대신 Metal을 Gate로 사용해 Depletion 영역을 없애 주어 Cap 값을 높게 유지시켜 줌 (주로 TaN, TiN 사용)

하지만 Metal Gate의 Work Function에 따라 다양한 이슈가 있음.

높은 Work Function을 가지는 Pt는 열적 안정성이 우수하지만 식각이 어렵고,

낮은 Work Function을 가지는 Al은 식각은 수월하지만 500도에서 Melting 된다는 단점이 있음.

즉, 공통적으로 열적 안정성이 우수해야하고, High K 소재와 접착성이 좋아야 하며, 기존 공정이 적용되고, 기생 Cap 문제가 없어야하고, 저항이 낮고,

증착 및 식각기술이 쉬워야 함. -Body Effect도 개선 가능

+HfO2 사용의 특징

두께 5배 가능, But SiO2와 달리 균일하기 어렵고, Si와 접착력이 낮아 ALD로 증착

+Poly Si의 도핑 농도를 계속 올릴 수 없는 이유 (Metal Gate 사용 이유)

Poly Si는 Metal과 달리 도핑으로 Workfunction을 제어할 수 있고(문턱 전압 조절), SiO2와 접착성이 좋아 많이 사용되었으나 도핑 농도가 너무 높으면 Dopant끼리 공유결합을 하며 Crystallization이 일어나 저항이 증가

Si 와 High K 유전체가 만날 경우 SiO2가 생성되어 기생 Cap이 발생해 Oxide Cap을 낮춤. - 일함수 제어의 한계

이에 따라 High K 유전체를 사용할 경우 Metal을 이용함.

SOI (Silicon on Insulator) (Single - Double Gate 순으로 발전, 즉, 3D 구조화)

HKMG 개선! Wafer 위에 Insulator 산화막(Buried Oxide)을 형성한 뒤, 그 위로 Si layer(Body) 영역을 형성한 것.

공정이 복잡하고 비싸지만 전체적인 비용은 저렴, 속도/성능/전력 소모/SS/Mobility 개선.

Bulk형 CMOS 기술(기존 MOSFET) 대비 우수. Depletion 영역의 Cap 값을 낮출 수 있음(기생 Cap 거의 0), Leakage 감소. S/D는 Raised가 필수적으로 필요함, Latch UP 억제: Well 구조로 인한 소자 오작동

1. PD (Partially Depleted): 잘 안 쓰임, SOI 위쪽의 Body Thickness가 두꺼워 부분적으로 Depletion.

기존 Bulk와 다르게 기판쪽으로 나가야 할 정공들이 나가지 못해 쌓이는 Floating Body Effect가 발생.

이는 Vth를 낮추고 Current Kink Effect 를 발생 시킴(전류 튐)

2. FD (Fully Depleted): 주로 사용. Body Thickness가 얇아(Ultra-Thin Body, UTB) 전체적으로 Depletion -삼전 Legacy 공정에 사용 (28나노)

정공이 쌓인 부분(Floating Body Effect)을 제거하여 Vd에 의해 전류가 급격히 증가하는 것을 억제할 수 있음. (Floating Body Effect 억제)

SON (silicon On Nothing): Silicon에 빈 공간을 만드는 것. (void처럼 생김), leakage의 이동 경로인 Source-Channel-Drain에 구멍을 뚫어 차단.

그 이유는 Si의 유전상수인 11.7보다 공기의 유전상수인 1이 훨씬 작아 전계의 밀도가 낮아지면서 Leakage를 줄일 수 있음.

FinFET 28nm~5nm 공정에 사용. Planar HKMG 공정의 한계 해결, 3D 공정으로 물고기 지느러미(Fin) 모양.

Gate가 Channel과 닿는 부분을 넓혀 2~3방향으로 전류가 흐를 수 있어 공간 효율 우수. (=집적도 우수).

수도꼭지가 2~3방향으로 있다고 생각하기. Gate 길이를 더 줄일 수 있고, Leakage를 획기적으로 제한 가능.

But 공정이 복잡해짐(작은 결함도 큰 문제). 방향에 따라 문턱전압이 다를 수 있음,

NMOS (100)의 경우 옆면이 110이기 때문에 Mobility 감소->45도 기울임

Fin도 Body 영역이기 때문에 FD상태가 되어야 Leakage 감소 가능.

+추가 공정

Double Gate 방식이 소자가 작아지며 공정 시간과 과정이 증가해 원가절감의 이점이 감소되면서 Tri Gate 방식 도입.

이 방법은 Fin이 너무 얇지 않아도 소자의 특성이 정상적으로 작동할 수 있음. 즉, 공정 난이도가 감소함. 삼전 7nm, 10nm, TSMC 5nm까지 사용

GAAFET (Gate All Around FET) 삼전 5nm 이하 공정 필수! 특히 SRAM

FinFET 개선! Nanowire를 사용해 Gate의 4면이 만나는 Gate

소형화에 유용하고, Multi-Channel이 가능해 Control이 용이. On Current 극대화 가능

누설전류가 적음, 공정의 난이도가 높음. ALD 공정을 통해 미세한 부분 증착!

++SRAM (Static Random Access Memory)

휘발성(=DRAM), Refresh 불필요(!=DRAM), 복잡, 집적도가 낮음, 비쌈 -> Low Memory or Cache Memory

MBCFET (Multi Bridge Channel FET) 삼전의 5nm이하 공정 기술, 3nm공정에 활용! HPC 등

GAAFET 개선! Nanowire 대신 Nanosheet를 이용해 연속적인 값 (면적)으로 성능 조절 가능, On Current 더욱 극대화, 고속.

설계 유연성이 매우 높음 - FinFET 공정과 호환성이 높아 기존 장비와 기술을 사용할 수 있음.

=> PPA(Power, Performance, Area) 극대화

++ DTCO (Design-Technology Co-Optimization): PPA 극대화를 위한 활동을 통칭.

++CAPA (생산 역량, 캐파), 이를 위한 기술이 개발되어야 함

BSPDN (Back Side Power Delivery Network)

Wafer의 전면부 만을 사용하는 FSPDN (Front Side Power Delivery Network)와 대비되는 개념.

즉, Wafer의 후면부를 사용.

FSPDN은 모든 기능이 전면부에만 있어 한정된 공간에 패터닝 해야 하므로 공정 난이도가 높음.

하지만 BSPDN은 전면부에는 Logic등 주요 기능을 넣고, 후면부에는 Power 배분, 신호 라우팅 등의 기능을 추가하는 것으로

FSPDN 대비 성능개선, 전력효율성 증가, Logic 속도 증가, 효율성 증가 예상 CMP, EDS, Packaging 기술의 발전이 중요하게 떠오르고 있음.

SOD (Spin On Dielectrics):

Tr이 상호작용 없이 정상적으로 동작하게 하는 Tr간의 격리기술이 중요해지면서 Tr 사이와 반도체 층간 Dielectric 시켜주는 Coating 소재.

SOH (Spin On Hardmasks)

PR하부에 적용되는 막질(얇아진 PR을 보호해주기 위해 - Etch 내성 증가)로서 후속 에칭 공정에서 적절한 방어막 역할을 수행하며,

미세 패턴의 정확도를 구현하기 위하여 회로가 원하는 막질에 잘 전사되도록 돕는 보조 재료

기존 공정인 CVD 대비 Spin Coating을 사용하기 때문에 높은 수준의 품질개선,

생산성 향상과 설비투자 비용 절감을 가능하게 해주는 핵심 소재. 안정성이 높고 장기보관이 가능.

++기존 공정과 비교

기존-CVD활용 Hard Mask

| PR |

| BARC |

| SiON |

| ACL (Amorphous Carbon Layer) |

ACL : Selectivity 개선 => 상당히 얇은 PR로도 패터닝 가능.

개선-SOH

| PR |

| S-SOH (Silicon) |

| C-SOH (Carbon) |

ARC의 특징도 보유

+ACL(Amorphous Carbon Layer):

Hardmask 제조 기술. 기판에 패턴을 형성할 때 미세화 되면서 패턴 붕괴가 발생.

이를 방지하기 위해 PR 형성 이전에 기판 위에 CVD를 이용해 형성. Etching Mask로 탁월한 역할. 하지만 공정이 느리고 Defect형성 가능.

=> Spin Coating(SOH) 주로 사용

iFET (Impact ionization FET)

일반 MOSFET의 HCI에서 발생하는 현상인 Impact ionization을 이용한 방법.

Complementary I MOS를 구현하기 위해 Source와 Drain의 Doping Type이 다름.

Gate의 위치에 따라 작동하는 곳이 달라지고, 이를 통해 SS가 감소할 수 있음. (가파름)

하지만, HCI의 단점과 함께 Vg값이 커야 하며 aging이 가속화.

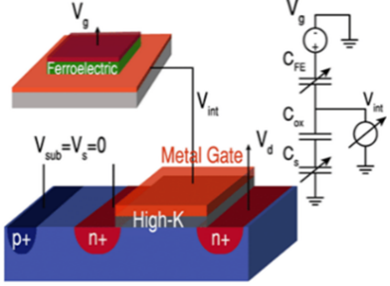

NCFET (Negative Capacitance FET)

SS의 60mV/dec의 한계를 극복하고자 하는 소자. Cap의 값을 음의 값을 취하면서 SS의 값을 작게 만드는 방법.

High K 유전체인 HfO2에 Zr(지르코늄)을 도핑해 강유전체(Ferro Electric)특성을 가지는 소재가 되어 음의 Cap 값을 가질 수 있음.

약 30mV/dec까지 가능하다고 함.

TFET (Tunneling FET)

SS의 60mV/dec의 한계를 극복하고자 하는 소자. Source와 Drain의 Doping Type이 다름.

Source에서 Channel로 carrier가 이동하는 방식을 Diffusion이 아니라 Tunneling 방식 사용.

Suspended Gate MOSFET

용수철 같은 기능을 적용한 Cantilever로 기계적으로 On/Off Control 진행. SS 개선을 위한 최초의 스위칭 기능 보유.

즉, 0, 1을 표시할 때 유리 (메모리로서 유리하지만 논리소자로서는 좋지 않다.)

붙일 때와 떨어트릴 때 전압 차이가 발생할 수 있음 -> Double Gate T FET (위아래 붙으면서 온오프)

Groove FET

Gate의 길이를 확장시켜 기판과 Drain 사이의 커패시턴스를 줄여 줌. 즉, SCE를 줄일 수 있음 - FinFET 공정 전 단계

++새로운 소재 도입 이슈 - 미세화 한계 1.5nm로 예상: Si를 대체할 소재를 활용한 공정을 만들어 내야 할 필요성이 대두. 그래핀, Ge등

+그래핀

세상에서 가장 얇은 소재, 탄소가 육각형 형태로 반복 연결된 평평하고 얇은 소재

장점: 열과 전기전도성(Si 100배 이상)이 좋음, Flexible 높음, 단단함, 안정성, 가격이 낮음

단점: Bandgap이 없어 도체이기에 활용이 어려움

+홀리그래파인 Metal Layer 위에서 CVD로 형성. Si의 Bandgap을 가지면서 그래핀의 전기전도도를 가지고 있는 소자.

'반도체 > Wafer 및 소자(Device) 기초' 카테고리의 다른 글

| [시스템 반도체] 시스템 반도체 종류 (3) | 2024.09.02 |

|---|---|

| [소자 정리] MPW, TSV 공정, Leakage 정리 (1) | 2024.09.02 |

| [문턱 전압] 문턱 전압, Threshold Voltage (1) | 2024.09.02 |

| [Transistor] Transistor, 트렌지스터 (4) | 2024.09.02 |

| [Epitaxy] Epitaxy 공정 (3) | 2024.09.02 |